Bei Hochleistungsprozessoren ist mit dem klassischen Chip-Design das Ende der Fahnenstange erreicht. Eine weitere Performance-Steigerung lässt sich nur nach oben – in die dritte Dimension erreichen. AMD ist hier Vorreiter und hat bereits erste Prozessoren mit 3D-Integration auf den Markt gebracht.

Schneller, höher, weiter. Die permanente Steigerung der Prozessorleistung scheint seit Beginn des Computerzeitalters eine der wenigen Konstanten in der IT zu sein. Dank dieses scheinbar ewigen Trends bietet jede neue CPU-Generation - und damit jede neue Generation von Servern, PCs und Notebooks - ein Performance-Plus, die Leistung pro Dollar wird mit jeder Generation besser. Und das bei gleichzeitig sinkenden Preisen.

Nun aber scheint die Chip-Industrie tatsächlich an eine Grenze gekommen zu sein, die das Mooresche Gesetz aushebelt. Vor allem mit zwei Problemen sind die Chip-Designer konfrontiert: Zum einen verlangsamt sich die Fähigkeit, Transistoren und die aus ihnen bestehenden Logik- und Speicherblöcke zu verkleinern. Zum anderen haben die Chips ihre Größengrenzen erreicht. Fotolithografie-Werkzeuge können nur eine Fläche von etwa 850 Quadratmillimetern strukturieren, was in etwa der Größe eines Nvidia-Grafikprozessors der Spitzenklasse entspricht.

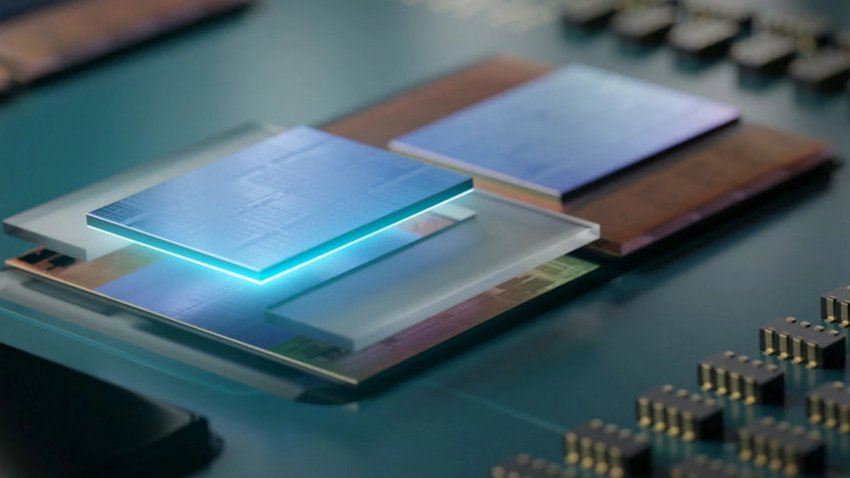

Dank des menschlichen Erfindungsreichtums deutet sich aber auch für diese Herausforderung eine Lösung an – mit dem Weg in die dritte Dimension. Die drohende Grenze der stetigen Verkleinerung der Chip-Strukturen in der zweidimensionalen Ebene überwinden die Entwickler mit dem Gang in die Höhe - indem sie vereinfacht gesagt einen Chip über einen anderen stapeln. Wenn zwei Chips direkt miteinander verbunden werden, lassen sich Tausende von Verbindungen pro Quadratmillimeter herstellen.

In der Elektronik nennt man die Methode, elektronische Komponenten sowohl horizontal als auch vertikal in zwei oder mehr Schichten zu integrieren, 3D-Integration oder 3D-Stacking. Sie wird in der Halbleiterindustrie als erfolgversprechender Weg gehandelt, den Trend kompakterer und leistungsstärkerer digitaler Geräte fortzusetzen („More than Moore“).

3D Chiplets: Der nächste Schritt

Um das 3D-Stacking praktisch umzusetzen, bedarf es allerdings einer Menge Innovationen. So müssen die Entwickler verhindern, dass die Wärme eines Chips im Stapel den anderen zerstört. Sie müssen entscheiden, welche Funktionen wohin gehören und wie sie hergestellt werden sollen. Weiter müssen sie dafür sorgen, dass ein gelegentlicher fehlerhafter Chip nicht zu vielen teuren Blindgängern führt. Und es muss geklärt werden, wie man mit der zusätzlichen Komplexität umgeht, die sich aus der gleichzeitigen Lösung all dieser Fragen ergibt.

AMD zeigt bei der 3D-Integration schon länger großes Engagement und kündigte bereits im März 2020 auf einer Analystenkonferenz an, dass es 3D-Stacking-Technologien mit "X3D" erforscht. Damals erklärte AMD, es handele sich um eine Mischung aus 2,5D- und 3D-Gehäusetechnologien, die eine 10-fache Bandbreitendichte oder mehr ermöglichen. Das "X" in "X3D" sollte für Hybrid stehen, und die Technologie war für "die Zukunft" vorgesehen.

Inzwischen hat sich die Zukunft „materialisiert“ und AMD hat die erste Stufe seiner 3D-Chiplet-Reise umgesetzt. Die erste Anwendung ist ein gestapelter „3D V-Cache“ auf einem Standard-Prozessorchiplet – was die Cache-Größe exorbitant erhöht. Die Steigerung der Cache-Größe ist für die Leistungsverbesserung ganz wesentlich, bestimmte Anwendungen können vom Zugriff auf einen größeren L3-Prozessor-Cache profitieren. Hierzu zählen speicherabhängige Anwendungen, Software, die häufig Cache-Misses aufweist, und Anwendungen mit größeren Datensätzen.

Die AMD 3D V-Cache Technologie löst die physikalischen Herausforderungen beim 2D-Chip-Design, indem sie den AMD Zen 3-Kern mit dem Cache-Modul verbindet und so den L3-Anteil bei gleichzeitiger Minimierung der Latenz und Erhöhung des Durchsatzes nutzt. Die V-Cache-Technik verwendet Through-Silicon Vias (TSVs) - vertikale Verbindungen durch ein Die hindurch - um oberhalb des regulären 32 MByte Level-3-Caches der Compute-Chiplets weitere zusätzliche Silizium-Cache-Stapel (die mit dem standardmäßigen 32-MB-L3-Cache-Bereich auf einem Chiplet thermisch verbunden sind) anzubringen.